DANG Nam Khanh

Associate Professor

- Affiliation

- Department of Computer Science and Engineering/Division of Computer Engineering

- Title

- Associate Professor

- khanh@u-aizu.ac.jp

- Web site

- https://u-aizu.ac.jp/~khanh/

Education

- Courses - Undergraduate

- PL03: JAVA Programming I (Ex.), Q1.

FU05: Computer Architecture (Ex.), Q1.

SE08: Introduction of Big Data Analytics (Ex.), Q3.

FU06: Operating Systems (Ex.), Q4.

- Courses - Graduate

- SYA14: Neuromorphic Computing, Q2.

RPW1: Research Paper Writing I, Q3+Q4.

Research

- Specialization

-

Control and system engineering

Electron device and electronic equipment

Computer system

Computational science

- Educational Background, Biography

-

Educational Background

- Ph.D. in Computer Science and Engineering, The University of Aizu, Japan, 2017

- M.Sc. in Information Systems & Technology, University of Paris-XI, France, 2014

- B.Sc. in Electronics & Telecommunications, Vietnam National University, Vietnam, 2011

Work Experience

- Associate Professor, The University of Aizu, 2022 April - now.

- Assistant Professor, Vietnam National University, Hanoi, 2017 November - 2022 March.

- Visiting Researcher, The University of Aizu, 2020 November - 2021 March.

- Visiting Researcher, The University of Aizu, 2019 May - 2019 September.

- Researcher, SISLAB, Vietnam National University, Hanoi, 2011-2014.

- RTL Designer, Dolphin Inc., 2010-2011.

- Current Research Theme

- - Neuromorphic engineering

- AI

- Low-power VLSI

- Key Topic

- Neuromorphic Computing, Faul-tolerance, VLSI, 3D Integrated Circuits, Generative AI

- Affiliated Academic Society

Others

- Messages for Students

- I firmly believe in mastering the fundamentals before tackling advanced topics. Take the time to read, study, and practice essential subjects like mathematics, English, and programming. This solid foundation will serve you well throughout your career. Remember, it’s better to build a strong base than a fragile structure.

Main research

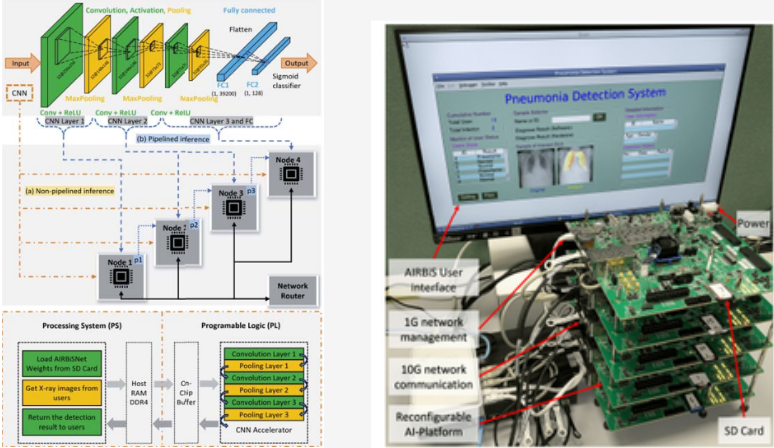

- Energy-Efficient Architectures: From Bio-Inspired AI SoCs to Green Computing

-

Our research in power and energy-efficient computing systems is essential to meeting the growing demand for more powerful and sustainable technology. As society increasingly relies on computing devices, managing their energy consumption becomes crucial. By developing efficient computing systems, we can significantly reduce energy costs, minimize environmental impact, and extend the battery life of portable devices. In large-scale data centers, enhancing energy efficiency leads to substantial cost savings and a reduced carbon footprint. Our work in this field fosters innovation in hardware and software design, paving the way for smarter, greener technologies that benefit both users and the planet.

...read more

- N-HuRo: Neuromorphic Humanoid Robotics

-

We investigate next‑generation adaptive distributed autonomous systems through the lens of anthropomorphic prosthetics, androids, and intelligent robotic platforms. Our research integrates cutting‑edge neuroscience, artificial intelligence, neuromorphic computing, and robotics to create highly responsive, lifelike systems capable of operating autonomously while adapting to human intent and dynamic environments.

Leveraging neuromorphic architectures and spiking neural networks, we develop control frameworks that enable natural, intuitive interaction between artificial limbs, androids, and biological systems. These brain‑inspired models support real‑time adaptation, low‑power operation, and seamless communication across distributed components.

Our work on non‑invasive neural interfaces allows prosthetic devices to adjust continuously to user intent, improving precision, comfort, and fluidity of motion. In parallel, our research on advanced sensory processing equips androids with human‑like perceptual capabilities, enabling them to interpret complex environmental stimuli, collaborate with humans, and function autonomously within distributed multi‑agent settings.

By bridging biomechanical engineering with AI‑driven cognition, we are advancing assistive technologies, human augmentation, and adaptive robotics. Our efforts extend to distributed anthropomorphic androids, where multiple embodied agents coordinate intelligently, share sensory information, and adapt collectively to real‑world tasks. This work lays the foundation for autonomous systems that are deeply integrated into daily life, scalable across environments, and capable of evolving with human needs.

...read more

Dissertation and Published Works

Selected Patents:

[P1] A. Ben Abdallah, Khanh N. Dang, An on-chip 3D system in which TSV groups containing multiple TSVs connect layers together [複数のTSVを含むTSVグループが層間を接続するオンチップの3次元システム], 特許第7488989号, Japan patent.

[P2] A. Ben Abdallah, Khanh N. Dang, Masayuki Hisada, TSV Error Tolerant Router Device for 3D Network On Chip, 特許第7239099号, Japan patent.

[P3] Khanh N. Dang, A. Ben Abdallah, ''Homogeneous computing system and migration flow generation program for homogeneous computing device” [ホモジニアスコンピューティングシステム及びホモジニアスコンピューティングデバイスのマイグレーションフローの生成プログラム], 特願 2022-196416, Japan patent, (patent pending)

[P4] Khanh N. Dang, A. Ben Abdallah, Nguyen Ngo Doanh1, ''Neural Network Processor'' [ニューラルネットワークプロセッサ], 特願 2024-047372, Japan patent, (filed patent).

Selected Publications:

[1] Ryoji Kobayashi, Ngo-Doanh Nguyen, Abderazek Ben Abdallah, Nguyen Anh Vu Doan and Khanh N. Dang, “ApproxiMorph: Energy-efficient Neuromorphic System with Layer-wise Approximation of Spiking Neural Networks and 3D-Stacked SRAM“, IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, 2025 (in-press). [DOI: 10.1016/10.1109/TCAD.2025.3597251]

[2] Ngo-Doanh Nguyen1, Khanh N. Dang, Akram Ben Ahmed, Abderazek Ben Abdallah, Xuan-Tu Tran, “NOMA: A Novel Reliability Improvement Methodology for 3-D IC-based Neuromorphic Systems“, IEEE Transactions on Components, Packaging and Manufacturing Technology, 2024 (in-press). [DOI: 10.1109/TCPMT.2024.3488113]

[3] Ngo-Doanh Nguyen, Akram Ben Ahmed, Abderazek Ben Abdallah, Khanh N. Dang, “Power-aware Neuromorphic Architecture with Partial Voltage Scaling 3D Stacking Synaptic Memory“, IEEE Transactions on Very Large Scale Integration Systems (TVLSI), vol. 31, no. 12, pp. 2016-2029, Dec. 2023.

[4] Khanh N. Dang, Nguyen Anh Vu Doan, Abderazek Ben Abdallah “MigSpike: A Migration Based Algorithm and Architecture for Scalable Robust Neuromorphic Systems”, IEEE Transactions on Emerging Topics in Computing (TETC), [DOI: 10.1109/TETC.2021.3136028].

[5] Khanh N. Dang, Akram Ben Ahmed, Abderazek Ben Abdallah, Xuan-Tu Tran, “HotCluster: A thermal-aware defect recovery method for Through-Silicon-Vias Towards Reliable 3-D ICs systems”, IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, IEEE, Volume 41, No. 4, pp. 799-812, April 2022. [DOI: 10.1109/TCAD.2021.3069370].

[6] Khanh N. Dang, Akram Ben Ahmed, Ben Abdallah Abderrazak and Xuan-Tu Tran, “TSV-OCT: A Scalable Online Multiple-TSV Defects Localization for Real-Time 3-D-IC Systems”, IEEE Transactions on Very Large Scale Integration Systems (TVLSI), IEEE, Volume 28, Issue 3, pp. 672 - 685, 2020. [DOI: 10.1109/TVLSI.2019.2948878].

[7] Khanh N. Dang, Akram Ben Ahmed, Yuichi Okuyama, Abderazek Ben Abdallah, “Scalable design methodology and online algorithm for TSV-cluster defects recovery in highly reliable 3D-NoC systems”, IEEE Transactions on Emerging Topics in Computing (TETC), IEEE, Volume 8, Issue 3, pp. 577-590, 2020. [DOI: 10.1109/TETC.2017.2762407].

[8] Khanh N. Dang, Akram Ben Ahmed, Xuan-Tu Tran, Yuichi Okuyama, Abderazek Ben Abdallah, “A Comprehensive Reliability Assessment of Fault-Resilient Network-on-Chip Using Analytical Model”, IEEE Transactions on Very Large Scale Integration Systems (TVLSI), IEEE, Volume 25, Issue 11, pp. 3099-3112, 2017. [DOI: 10.1109/TVLSI.2017.2736004].

For more details, please visit: https://u-aizu.ac.jp/~khanh/