Advanced of On-Chip Interconnects and 3D-ICs Technologies

Overview

Future System‑on‑Chip (SoC) platforms will integrate hundreds of heterogeneous components — processor cores, DSPs, memory blocks, accelerators, and I/O subsystems — within extremely compact silicon footprints. As integration density increases, these systems are evolving beyond traditional bus‑based communication toward sophisticated on‑chip networks and vertically integrated architectures.

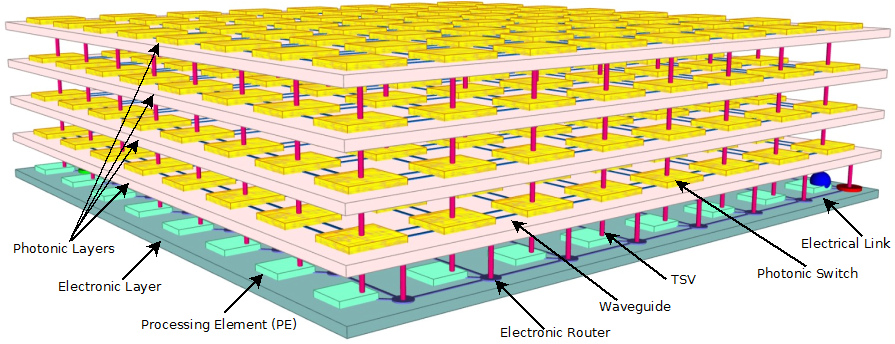

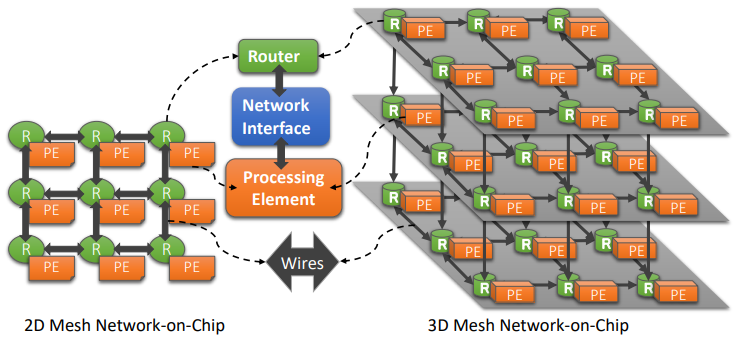

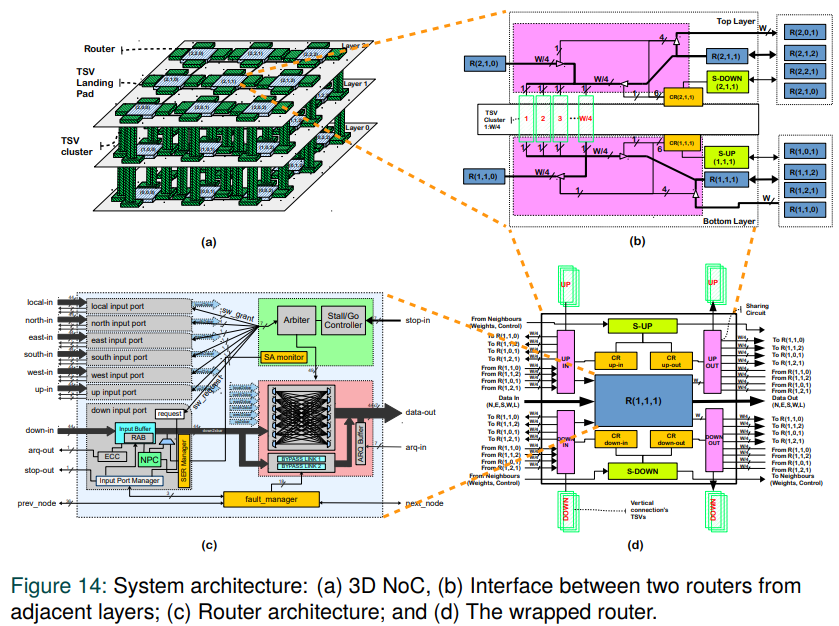

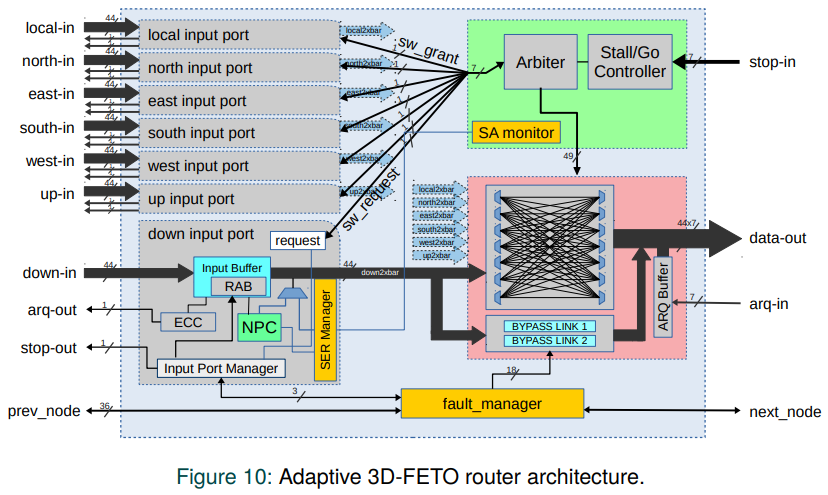

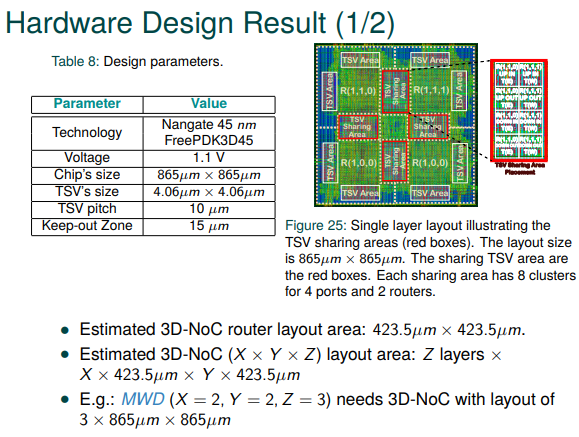

Our research addresses the key challenges of this transition by exploring advanced on‑chip interconnects and 3D‑IC technologies, including 3D chiplets, 2.5D/3D packaging, hybrid bonding, and photonic‑electronic interconnects. We investigate scalable and energy‑efficient 3D NoCs, AI accelerators with stacked memory, and reliability‑driven design methodologies to ensure robust operation in deep 3D stacks.

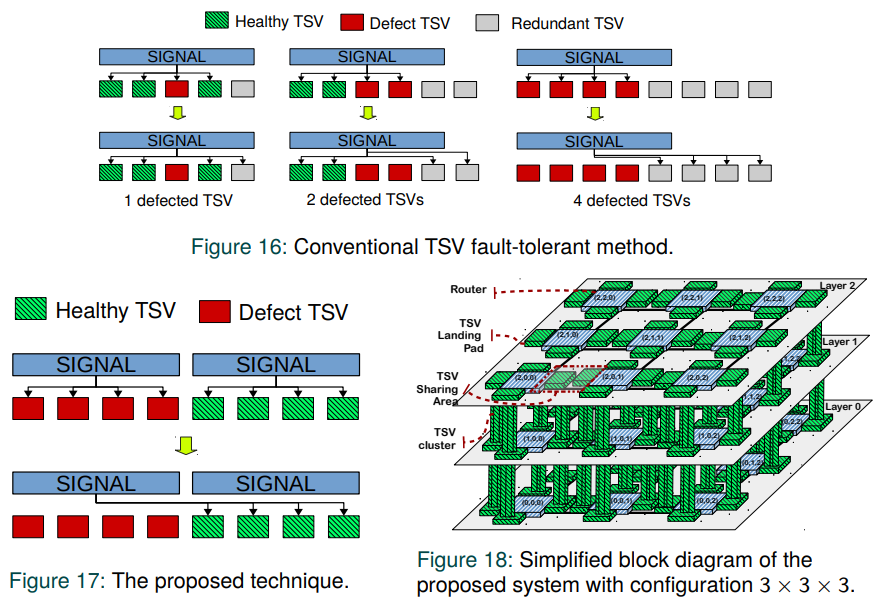

This work tackles critical issues such as fault tolerance, TSV‑based vertical integration, photonic communication, low‑power mapping, adaptive routing, and emerging reliability challenges inherent to next‑generation heterogeneous many‑core systems.

...read more