次世代AIシステムのためのエネルギー効率型ハイブリッドメモリアーキテクチャ(HYbrid MEmory based Architecture for NeXt-Generation AI Systems)

リンク:[JSPS 科研費]│[研究代表者 Researchmap]│[プロジェクトデータベース]│[プロジェクトページ(準備中)]

基本情報

- 資金提供:科研費(基盤研究B)

- 課題番号:26K02883

- 期間:2026年4月~2029年3月

- 予算:18,330,000円

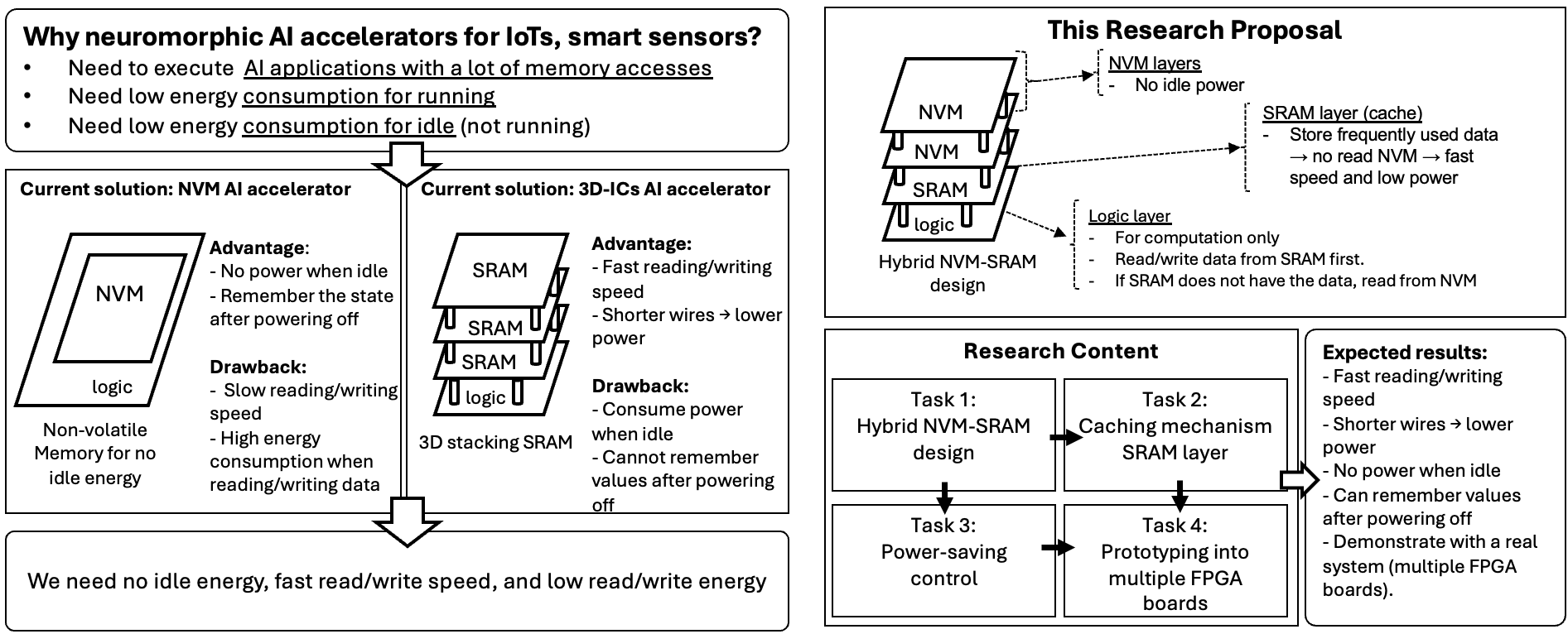

- 概要:人工知能(AI)は大きく進展してきた一方で、その高い消費電力は依然として深刻な課題であり、特にスマートフォン、IoTセンサ、バッテリー駆動や太陽光駆動のシステムなどの小型デバイスにおいて重要である。本プロジェクトでは、3次元集積回路(3D-IC)を用いて不揮発性メモリ(NVM)とSRAMを組み合わせた、新しい省エネルギー型ニューロモルフィックAIアクセラレータを提案する。NVMは電源なしでもデータを保持できるため待機時の消費電力を大幅に低減できるが、一般にSRAMに比べて読み書きが遅くエネルギー消費も大きい。この課題に対し、本研究ではロジック層の上にNVM層を積層してデータ転送距離を短縮し、さらにロジックとNVMの間に小型で高速なSRAMキャッシュ層を配置するハイブリッドメモリアーキテクチャを提案する。また、電力状況に応じてエネルギー使用を動的に調整する適応的電力管理技術を導入し、精度や性能への影響を最小限に抑える。これらの技術により、動作時および待機時の消費電力を削減し、スマートフォンやIoT機器、スマートセンサなどの実環境で利用可能な低消費電力AIチップの実現を目指す。

研究技術とプロトタイピング

本研究グループは、高効率AIハードウェアおよび次世代メモリ・コンピュートシステムの設計と検証を専門とする。業界最先端のAMD(旧Xilinx)FPGAプラットフォームを活用し、アーキテクチャ理論と実シリコン実装のギャップを橋渡しする。

コア手法

フルシステムプロトタイピング:AMD Xilinx環境において、Verilog/VHDLによるRTLベースの設計フローを採用する。これにより、サイクル精度でのハードウェア検証と複雑なニューラルアクセラレータの信頼性の高い性能評価を実現する。

3D-ICおよびインターコネクトエミュレーション:3D-IC製造の反復的検証の難しさを踏まえ、Network-on-Chip(NoC)機能を用いて高帯域な垂直インターコネクトおよびTSV(Through-Silicon Via)の遅延特性を模擬する。

先進メモリモデリング:不揮発性メモリ(NVM)や3次元積層型SRAM-NVMなどの新興技術について、タイミング、エネルギー特性、データ保持特性をモデル化するカスタムビヘイビアラッパーを開発する。

注:最終プログラムは将来的にMITライセンスでGitHubに公開予定。

メンバー

学生

2026年度

- HANYU Yuga

- SHARMA Atharv

- LUYEN Van-Vu

- KOMATSUZAKI Aruki

スケジュール

初期プロトタイピング(2026年度以前)

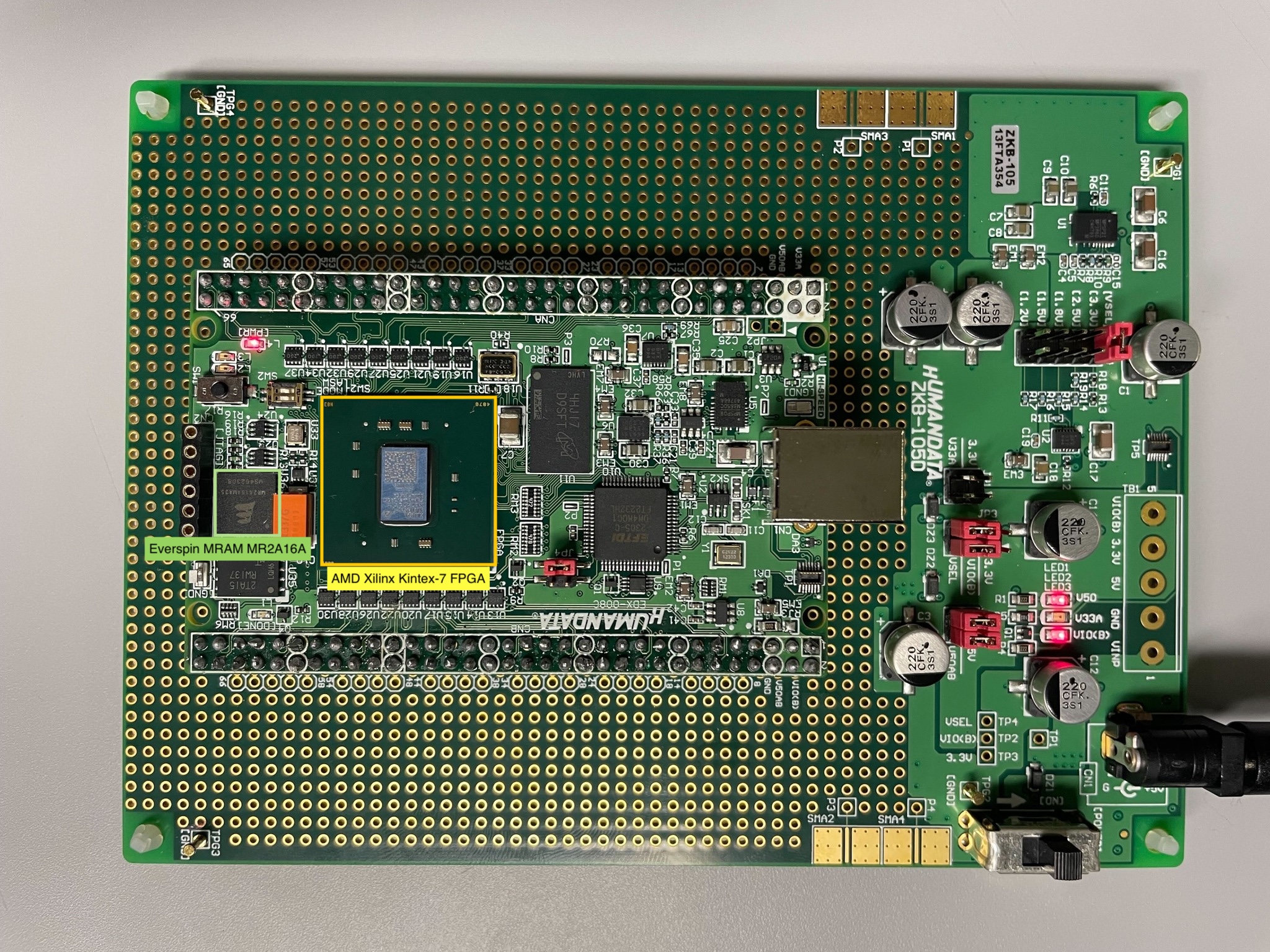

初期プロトタイピングとして、HumanDATA Kintex-7 EDX-008-70Tを用い、Everspin製MRAMの読み書きを検証した。

全体スケジュール

連絡先

- khanh [at] u-aizu.ac.jp

資金提供