齋藤 寛 SAITO Hiroshi

教授、コンピュータ工学部門長

- 所属

- コンピュータ理工学科/コンピュータ工学部門

- 職位

- 教授、コンピュータ工学部門長

- hiroshis@u-aizu.ac.jp

教育

- 担当科目 - 大学

- 論理回路設計論、論理回路設計特論、システム総合演習I

- 担当科目 - 大学院

- Electronic Design Automation for System-level Design、Design Automation for Digital VLSIs

研究

- 研究分野

-

電子デバイス及び電子機器

知能情報学

非同期式回路の設計自動化、エッジAIデバイスの設計、野生動物警報システムの開発

- 略歴

- 1998 会津大学卒業 2000 会津大学大学院博士前期課程修了 2003 東京大学大学院工学系研究科博士後期課程修了(工学博士) 2003-2004 東京大学先端科学技術研究センター特任助手 2004-2007 会津大学講師 2007-2012 会津大学准教授 2012-2021 会津大学上級准教授

- 現在の研究課題

- 研究分野と同じ

- 研究内容キーワード

- Asynchronous circuits, FPGA, edge AI

- 所属学会

- IEEE、ACM、電子情報通信学会、情報処理学会

パーソナルデータ

- 学生へのメッセージ

- 将来の自分の目標に向けて一緒に頑張りましょう

主な研究

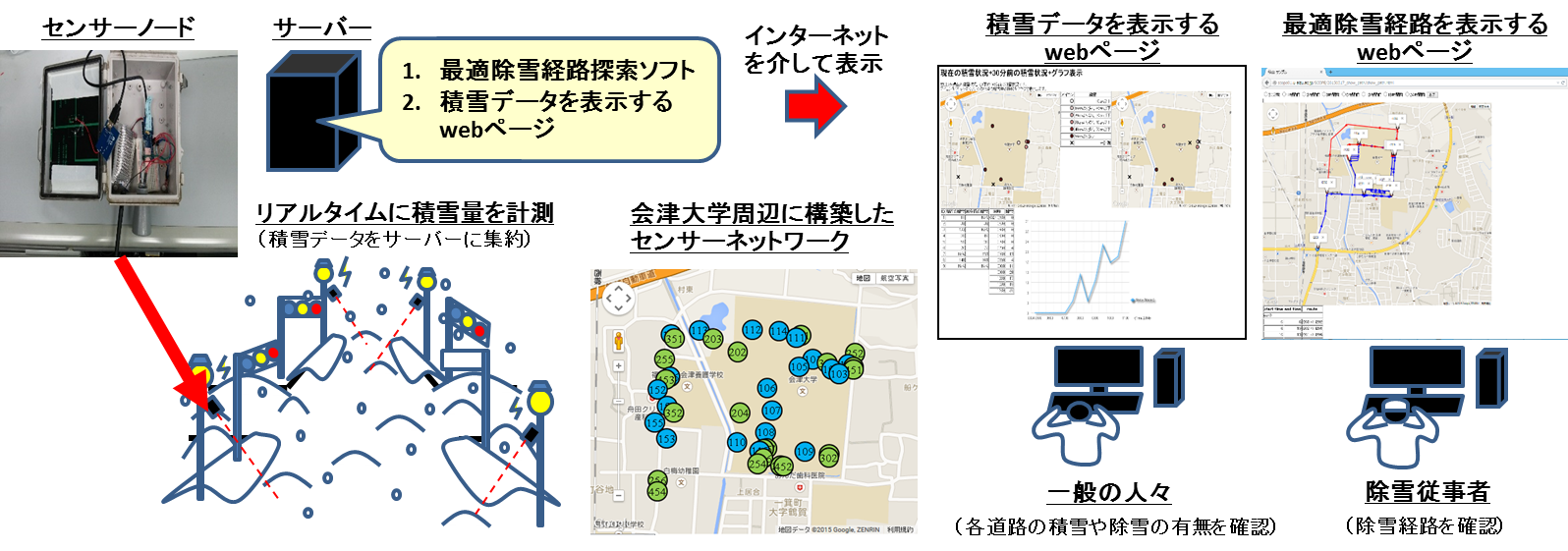

- オープンソースハードウェアとセンサーネットワークによる積雪の可視化と除雪支援

-

〇目的

冬になると雪による災害(交通事故、雪崩、交通・流通の麻痺)が後を絶たない。こうした災害を減らすためには、降雪の初期段階からリアルタイムで積雪を監視し、備えを行うことが大切となる。本研究では、オープンソースハードウェアArduinoと無線モジュールXBeeを用いてセンサーネットワークを構築し、定期的にセンシングされた積雪データをwebページ上で可視化する。また最適な除雪経路を探索するソフトウェアを開発する。

〇これまでの成果と今後の課題

本研究は平成25-26年度に総務省のSCOPEに採択された「オープンソースハードウェアとセンサーネットワークによる除雪支援システム」がベースとなっている。これまでにセンサーネットワークの構築、webページ開発、最適な除雪経路を探索するソフトウェアの開発、実証実験を行っており、今後はセンサーネットワークの範囲拡大、バッテリー寿命の延長、webページや除雪経路を探索するソフトウェアの改善を行っていく。

- 非同期式回路の設計支援技術 ~低消費電力・低電磁放射な回路を自動で生成~

-

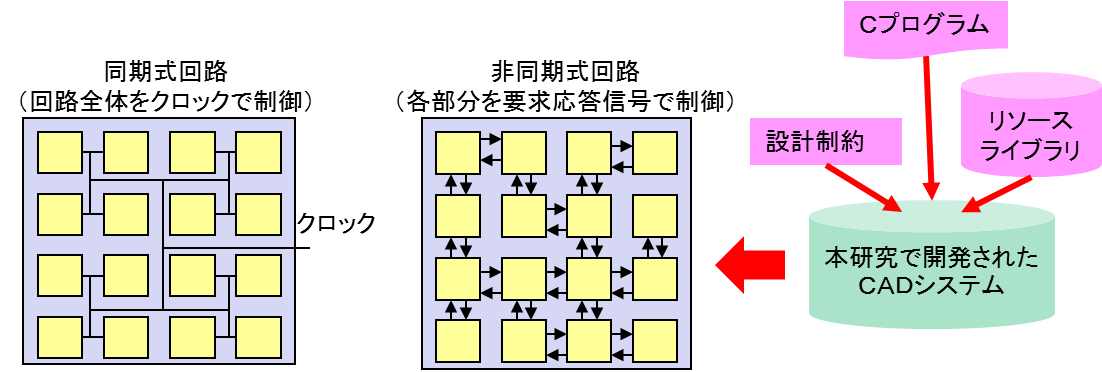

〇背景

現在の組み込みシステムのほとんどは、クロック信号と呼ばれるグローバルな信号を用いて回路全体を制御する同期式回路として実現されている。しかしながら、集積回路の微細化技術が向上するにつれ、クロック信号自身の消費電力の増加、回路全体が一斉に動作することによる電磁放射の増加などが深刻な問題となる。

〇非同期式回路とは?

非同期式回路は、同期式回路とは異なり、ローカルな要求応答信号を用いて回路を制御する。クロック信号を用いないため、クロック信号にまつわる問題がない。また、ローカルな要求応答信号によって必要な時に必要な部分が動作するので、潜在的に低消費電力、低電磁放射である。しかしながら、同期式回路と比べ非同期式回路の設計は困難である。用途に応じて適切な回路モデルを選ぶ必要がある。また、選ばれた回路モデルによって、設計手法が異なる。

〇目的

本研究では、C言語によって記載されたアプリケーションの仕様記述より、面積や性能などの設計制約を満たす最適な非同期式回路を自動で設計する設計支援CADシステムを開発する。

主な著書・論文

1. Hideki Katabami, Hiroshi Saito, Tomohiro Yoneda, "Design of a GALS-NoC using Soft-cores on FPGAs" Proc. 2013 IEEE 7th International Symposium on Embedded Multicore Mancore System-on-Chip (MCSoC), pp.31-36, September 2013.

2. Minoru Iizuka and Hiroshi Saito, "A floorplan method for ASIC designs of asynchronous circuits with bundled-data implementation" Proc. 2013 IEEE 11th International New Circuits and Systems Conference (NEWCAS), pp.1-4, June 2013.

3. Minoru Iizuka, Naohiro Hamada, and Hiroshi Saito, "An ASIC Design Support Tool Set for Non-pipelined Asynchronous Circuits with Bundled-Data Implementation"IEICE Transactions on Electronics, Volume E96-C No.4, pp.482?491, April 2013.

4. Hiroshi Saito, Tomohiro Yoneda, and Yuichi Nakamura, "An ILP-based Multiple Task Allocation Method for Fault Tolerance in Networks-on-Chip", Proc. IEEE International Symposium on Embedded Multicore SoCs, Septermber 2012.

5. Naohiro Hamada and Hiroshi Saito, "Integration of Behavioral Synthesis and Floorplanning for Asynchronous Circuits with Bundled-Data Implementation", IEICE Transaction, Volume E95-C No.4, pp.506?515, April 2012.

6. Minoru Iizuka, Naohiro Hamada, Hiroshi Saito, Ryoichi Yamaguchi, and Minoru Yoshinaga, "A Tool Set for the Design of Asynchronous Circuits with Bundled-data Implementation", International Conference on Computer Design 2011,pp.78?83, October 2011.

7. Naohiro Hamada and Hiroshi Saito, "Integration of Behavioral Synthesis and Floorplanning for Asynchronous Circuits with Bundled-data Implementation", GLS VLSI'11 VLSI,pp.157?162, May 2011.

8. Hiroshi Saito and Naohiro Hamada, "A floorplan method for asynchronous circuits with bundled-data implementation on FPGAs", International Symposium on Circuits and Systems (ISCAS 2010),pp.925?928, May 2010.

9. Naohiro Hamada, Yuuki Shiga, Takao Konishi, Hiroshi Saito, Tomohiro Yoneda, Cris Myers, and Takashi Nanya, "A Behavioral Synthesis System for Asynchronous Circuits with Bundled-data Implementation", IPSJ Transaction on System LSI Design Methodology, no.2, pp.67?79, Feburary 2009.