集積回路の自動設計技術 ~設計規則・設計仕様を満たす回路を 自動で設計する技術の開発~

概要

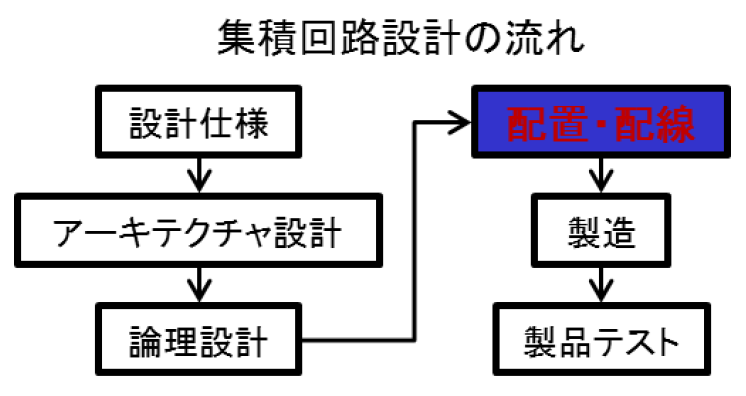

〇現在の集積回路の規模は非常に大きく、人手のみによる設計は不可能である。多くの設計過程において、自動設計技術が用いられており、自動設計技術の性能が製造される回路の性能に大きく影響します。我々は、集積回路の自動設計技術、特に記憶素子の配置・記憶素子間の配線に関する研究を行っています。

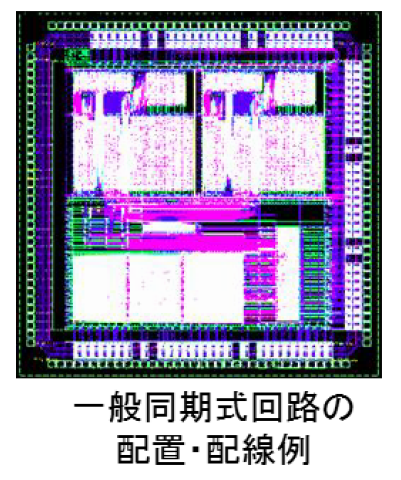

〇一般同期式回路の自動設計技術

現在の集積回路では、クロック信号を各記憶素子に同じタイミングで供給しているため、消費電力、電磁放射など様々な問題を抱えている。各記憶素子にクロック信号を供給するタイミングを分散させることが可能な一般同期式回路は、これらの問題を解決すると期待されている。現在、与えられた動作速度、消費電力などの設計仕様を満たす一般同期式回路の自動設計技術の開発に取り組んでいます。

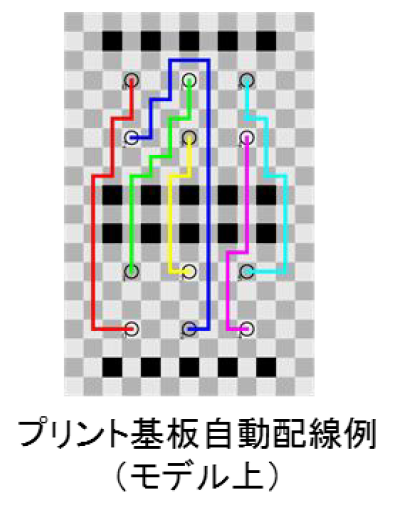

〇プリント基板の自動配線技術

複数の集積回路を接続するプリント基板は、基板の設計規則だけでなく、各集積回路から決められる設計仕様を満たさなくてはならない。最近の集積回路設計では、微細化、高速化により、特にタイミング制約が厳しくなってきている。現在、複雑化する設計規則・仕様・制約を満たすプリント基板配線を自動設計する技術の開発に取り組んでいます。